# An AADL-DEVS Framework for Cyber-Physical Systems Modeling and Simulation Supported with an Integrated OSATE and DEVS-Suite Tools

Ehsan M. Ahmad College of Computing and Informatics, Saudi Electronic University, Riyadh, Saudi Arabia Hessam S. Sarjoughian

Arizona Center for Integrative Modeling & Simulation School of Computing, Informatics, and Decision Systems Engineering, Arizona State University, Tempe, Arizona, USA

March 9, 2020

| Contents |

|----------|

|----------|

| 1. | Intro | oduction | n                                                                     | 2  |

|----|-------|----------|-----------------------------------------------------------------------|----|

| 2. | Back  | kground  | I                                                                     | 2  |

|    | 2.1.  | System   | n-Theoretic Discrete-Event Simulation                                 | 2  |

|    |       | 2.1.1.   | Atomic DEVS Model                                                     | 2  |

|    |       | 2.1.2.   | Coupled DEVS Model                                                    | 3  |

|    | 2.2.  | DEVS     | Suite Simulator                                                       | 4  |

|    | 2.3.  | Archite  | ecture Analysis & Design Language                                     | 4  |

| 3. | AAI   | )L-DEV   | /S Framework                                                          | 6  |

|    | 3.1.  | AADL     | Modeling                                                              | 6  |

|    |       | 3.1.1.   | Structure Modeling                                                    | 7  |

|    |       | 3.1.2.   | Data Modeling                                                         | 7  |

|    | 3.2.  | Behavi   | or Modeling using DEVS Annex                                          | 8  |

|    |       | 3.2.1.   | Variables Section                                                     | 9  |

|    |       | 3.2.2.   | States Section                                                        | 9  |

|    |       | 3.2.3.   | Behavior Section                                                      | 10 |

|    |       | 3.2.4.   | External Transition Function                                          | 10 |

|    |       | 3.2.5.   | Internal Transition Function                                          | 11 |

|    |       | 3.2.6.   | Output Function                                                       | 12 |

|    |       | 3.2.7.   | Test Input Declaration                                                | 13 |

|    | 3.3.  | Code C   | Generation for Simulation                                             | 13 |

|    |       | 3.3.1.   | Data Classes Generation                                               | 14 |

|    |       | 3.3.2.   | Structural Code Generation                                            | 18 |

|    |       | 3.3.3.   | Behavioral Code Generation                                            | 19 |

|    |       | 3.3.4.   | Code Generation for Composite Components                              | 23 |

| 4. | A Ca  | ase Stuc | ly of Isolette Thermostat System                                      | 23 |

|    | 4.1.  | Manag    | e Regulator Interface Function                                        | 25 |

|    |       | 4.1.1.   | Data Specification                                                    | 25 |

|    |       | 4.1.2.   | Functional Requirements Specification                                 | 26 |

| 5. | Man   | age Re   | gulator Interface Modeling & Simulation under the AADL-DEVS Framework | 26 |

|    | 5.1.  | Structu  | re and Data Modeling                                                  | 27 |

|    |       | 5.1.1.   | Manage Interface Failure & Desired Range                              | 27 |

|    |       | 5.1.2.   | Manage Display Temperature                                            | 28 |

|    |      | 5.1.3.  | Manage Status                            | 29 |

|----|------|---------|------------------------------------------|----|

|    |      | 5.1.4.  | Manage Regulator Interface               | 30 |

|    | 5.2. | Behavi  | or Modeling                              | 31 |

|    |      | 5.2.1.  | Manage Interface Failure & Desired Range | 31 |

|    |      | 5.2.2.  | Manage Display Temperature               | 32 |

|    |      | 5.2.3.  | Manage Status                            | 34 |

|    |      | 5.2.4.  | Manage Regulator Interface               | 35 |

|    | 5.3. | Code (  | Generation for DEVS Simulation           | 35 |

|    |      | 5.3.1.  | Manage Interface Failure & Desired Range | 35 |

|    |      | 5.3.2.  | Manage Display Temperature               | 40 |

|    |      | 5.3.3.  | Manage Status                            | 43 |

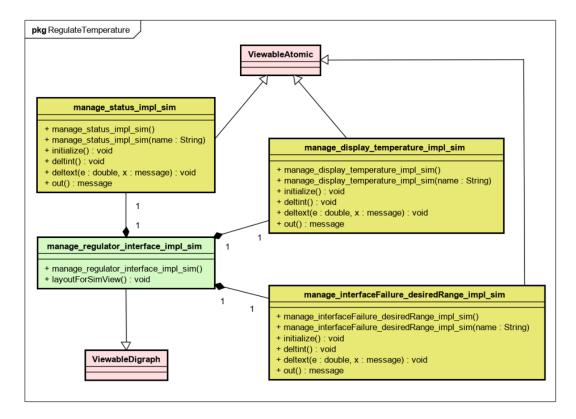

|    |      | 5.3.4.  | Manage Regulator Interface               | 45 |

| 6. | Simu | ulation | using DEVS-Suite                         | 46 |

|    | 6.1. | Atomi   | c Model Simulation                       | 46 |

|    | 6.2. | Couple  | ed Model Simulation                      | 46 |

| 7. | Rela | ted Wo  | rk                                       | 47 |

| 8. | Con  | clusion | and Future Work                          | 48 |

| A  | DEV  | S Anno  | ex Syntax Card                           | 50 |

|    | A1.  | Lexica  | l Elements                               | 50 |

|    | A2.  | Gramn   | nar Productions                          | 51 |

## List of Figures

| 1  | Graphical notation for Atomic and Coupled Models in DEVS-Suite Simulator                 | 4  |

|----|------------------------------------------------------------------------------------------|----|

| 2  | Graphical notation for hierarchical modeling in AADL                                     | 5  |

| 3  | AADL-DEVS Framework                                                                      | 6  |

| 4  | AADL to DEVS Code Generation Engine (ADCoDE) Workflow                                    | 14 |

| 5  | Class diagram for primitive data types                                                   | 15 |

| 6  | Class diagram for compound data types                                                    | 15 |

| 7  | Newly generated class <i>current_speed</i> being used within <i>regulate_speed</i> class | 18 |

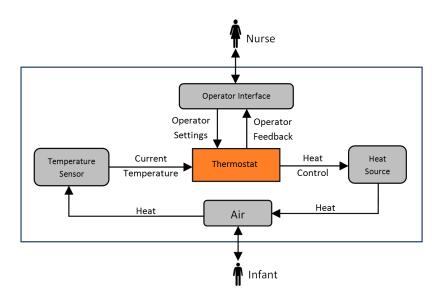

| 8  | Isolette Context Diagram with Controller (Thermostat) and Physical Environment (Air)     | 24 |

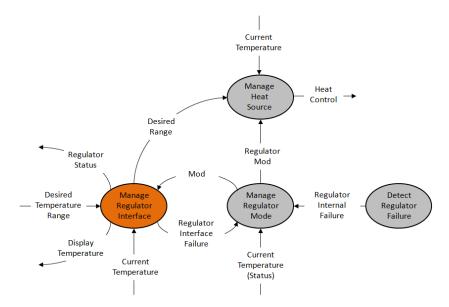

| 9  | Regulate Temperature Function                                                            | 25 |

| 10 | Manage Regulate Interface AADL model                                                     | 27 |

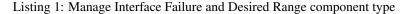

| 11 | Manage Regulate Interface UML class diagram                                              | 47 |

| 12 | Manage Regulate Interface Coupled DEVS model                                             | 48 |

### List of Tables

| 1 | Commission data temperanishing | und in the Manage Descilator Interface | 25     |

|---|--------------------------------|----------------------------------------|--------|

| 1 | Complex data type variables    | used in the Manage Regulator Interface | <br>25 |

## Listings

| Manage Interface Failure and Desired Range component type                                    | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manage Display Temperature component type                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Manage Interface Failure and Desired Range component implementation                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Manage Display Temperature component implementation                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Manage Status component implementation                                                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Data class generated for <i>lower_desired_temperature</i>                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Model class generated for thread manage_interfaceFailure_desiredRange with thread implemen-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| tation manage_interfaceFailure_desiredRange_impl                                             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Data class generated for <i>current_temperature</i>                                          | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Model class generated for thread manage_display_temperature with thread implementation man-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| age_display_temperature_impl                                                                 | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Model class generated for thread manage_status with thread implementation manage_status_impl | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Model class generated for thread manage_regulator_interface with thread implementation man-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| age_regulator_interface_impl                                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                              | Manage Display Temperature component typeManage Status component typeManage Regulator Interface component typeManage Regulator Interface component typeManage Interface Failure and Desired Range component implementationManage Display Temperature component implementationManage Status component implementationManage Regulate Interface component implementationManage Regulate Interface component implementationData class generated for lower_desired_temperatureModel class generated for thread manage_interfaceFailure_desiredRange with thread implementationData class generated for thread manage_implData class generated for thread manage_display_temperatureModel class generated for thread manage_display_temperature with thread implementation manage_status_implModel class generated for thread manage_regulator_interface |

#### Abstract

The continuing rise of complexity in mixed computational and physical systems demands dynamical models representing structure and behavior together. The software and, more broadly, system architectures are essential in tackling high-level complexity. System architectures are used to define the structures of components and their relationships. Architecture specifications focus on the requirements and static aspects of systems. The specifications detailing the behavioral complexity of the components and their interactions are needed. Design specifications define how components should react to the external stimuli it may receive over some period of time. Therefore, the architecture and design specifications serve complementary roles in model-based design and virtual experimentation.

The Architecture Analysis & Design Language (AADL) and Discrete Event System Specification (DEVS) are proposed as complementary methods for developing, in a step-wise fashion, architecture and design models. The proposed AADL-DEVS framework is grounded in the foundational modularity and hierarchy principles that are common to the DEVS and AADL modeling methods.

A DEVS Annex (DA) is specified according to the DEVS specification for AADL. This annex supports defining discrete-event component structure and behavior in terms of state transition functions with and without external inputs, output functions, and time advance functions. The DA is defined according to the DEVS-Suite simulator which conforms to the parallel DEVS specification. The Open-Source AADL Tool Environment (OSATE) is extended according to the DEVS-Suite simulator. An implementation of this framework supports translating AADL-DEVS models to models that can be simulated in the DEVS-Suite simulator. The Eclipse-based AADL-DEVS framework is developed to afford as much as possible seamless AADL to DEVS model development and simulation.

The DEVS Annex modeling in OSATE and its simulation in the DEVS-Suite simulator are demonstrated using a model of an infant incubator, a time-critical and safety-critical system. This system exhibits reactive computation, concurrency, and feedback control for Cyber-Physical Systems and, more generally, Systems-of-Systems. The example demonstrates adding basic time-based behaviors to the components of an AADL model of the infant incubator. The simulation model and its execution are described. Selected related works, future work, and conclusion are described.

*Keywords*: AADL, Behavior Modeling, Cyber-Physical Systems, DEVS, DEVS Annex, DEVS-Suite, OSATE, Safety-Critical Systems

### 1. Introduction

Building Cyber-Physical Systems (CPS) or more broadly Systems-of-Systems (SoS) is challenging, in part, because of a variety of concepts, methods, frameworks, and tools that are needed to tackle their multifaceted nature [4, 38, 32]. Models that can be used together architectures and designs are challenging to develop in a seamless fashion. There are conceptual gaps in connecting, for example, across multiple specification abstractions.

The Architecture Analysis & Design Language (AADL) [9] and Discrete Event System Specification (DEVS) ([37] provide a foundation for developing specifications that cover and integrate high-level architectural and low-level design abstractions. That is, a key to the development of the Cyber-Physical Systems and Systems-of-Systems is to have specifications that can precisely represent decisions spanning both coarse-grain and fine-grain design needs. The former generally lends itself for characterizing architectures (i.e., components and their relationships) of systems. The latter supports theoretically grounded specifications for hierarchical component behaviors that conform to the defined system architecture specifications. This two-step process belonging to the full CPS and SoS life-cycle development involves combining structures and behaviors at multiple abstraction levels. These observations highlight the importance of addressing system structure and behavior complexity traits using integrated architecture and design models.

Grounded in the AADL and DEVS modeling methods, the rest of this report details the proposed and developed AADL-DEVS framework. Section 2. introduces atomic and coupled DEVS with DEVS-Suite simulator and AADL with its structure and behavior specification mechanism. Section 3. presents a detailed description of the proposed AADL-DEVS framework with descriptions of structure and data modeling using core AADL and behavior modeling using DEVS annex (DA). An AADL to DEVS CoDe generation Engine (ADCoDE) is described for automated simulation code for the DEVS-Suite simulator in this section. In Section 4., a case study on infant incubator (*Isolette*) system is presented to illustrate the use of the DA sub-language and demonstrate the use of the proposed AADL-DEVS framework for time- and safety-critical systems. Section 5. describes the modeling of the *Manage Interface Interface* component of the Isolette system in the AADL-DEVS framework while Section 6. describes the simulation of the component in the DEVS-Suite simulator. Section 7. presents a summary of the related work, and Section 8. summarizes this report.

#### 2. Background

This section presents an overview of the parallel DEVS formalism and the DEVS-Suite simulation framework. Emphasis is on basic atomic and coupled model specification constructs and their realization and execution in the DEVS-Suite simulator. Similarly, the basic concepts of the AADL framework and its implementation environment OSATE are presented. The elemental software and execution aspects of the AADL are highlighted.

#### 2.1. System-Theoretic Discrete-Event Simulation

The Discrete Event System Simulation (DEVS) is generally considered suitable for modeling and simulating systems [37]. Certain classes of software (e.g., [11]), hardware (e.g., [7]), and mixed software/hardware systems (e.g., [23]). As a mathematical formalism, it lends itself for specifying structures and behaviors of Systems of Systems (SoS) including Cyber-Physical Systems (CPS). This modeling formalism is based on the Systems Theory [35] where a system is defined in terms of hierarchical modules that are composed through their inputs and outputs. Models can have communicate arbitrary data types with arbitrary timing and data/event handling. As such, discrete and continuous dynamical systems as discrete event models. Moreover, DEVS can be used to describe any discrete event systems [37]. In DEVS, there are two types of model components: *atomic model* and *coupled model*.

#### 2.1.1. Atomic DEVS Model

A parallel DEVS atomic model is a mathematical structure as defined below

$$DEVS = \langle X^b, Y^b, S, Q, \delta_{ext}, \delta_{int}, \delta_{con}, \lambda, ta \rangle$$

<sup>(1)</sup>

where

$X^b$  is a set of input port names, each having a bag of values,

$Y^b$  is a set of output port names, each having a bag of values,

S is a set of sequential states,

Q is a set of *total states*  $\{(s, e) | s \in S, 0 \le e \le ta(s), e \text{ is the elapsed time}\},\$

$\delta_{ext}: Q \times X^b \to S$  is an external transition function,

$\delta_{int}: S \to S$  is the internal transition function,

$\delta_{con}: Q \times X^b \to S$  is an confluent transition function,

$\lambda: S \to Y^b$  is an *output function*, and

$ta: S \to \Re^+_{0\infty}$  is a time advance function.

The input and output ports with their values (i.e., primitive or compound messages) are used to specify the exterior structure of every atomic model. The internal behavior of an atomic model is specified in terms of a set of state variables and a set of functions. A model can have autonomous and reactive behaviors specified in terms of an *internal transition* function and an *external transition* function, respectively. The *output function* is for generating output messages for any number of output ports. The *time advance function* captures the timing of state transitions. The *confluent function* can be used for specifying simultaneous handling of internal and external events. An atomic model can have multiple input and/or output messages. The elapsed time *e* has the role of allowing external inputs to arrive at arbitrary time instances. The ta(s) = 0 allows instantaneous state change which is a basic capability for modeling concurrent and distributed software/hardware systems.

#### 2.1.2. Coupled DEVS Model

A parallel DEVS coupled model is a mathematical structure as defined below

$$CM = \langle X^b, Y^b, D, M_d | d \in D, EIC, EOC, IC \rangle$$

<sup>(2)</sup>

where

$X^b$  is a set of input port names, each having a bag of values,

$Y^b$  is a set of output port names, each having a bag of values,

D is a set of component names,

$M_d$  is a set of basic components for each  $d \in D$ ,

EIC is a set of external input couplings,

EOC is a set of external output couplings, and

IC is a set of internal couplings.

A coupled model is composed of one or more atomic and/or coupled models. The input and output ports and values have the same specification as the atomic model. The structure specification of a coupled model includes input & output ports, a set of components, and component coupling information. DEVS can ensure semantically identical input/output interfaces for atomic and coupled models. The coupling information is categorized as (1) the *external input coupling* (EIC) - coupling of coupled model input ports to input ports of some component, (2) the *external output coupling* (EOC) - coupling of component output ports to the coupled model output ports, and (3) the *internal coupling* (IC) - coupling of component output ports to input ports of components. A coupled model behavior is based on the message exchanges between itself and its components as well as message exchanges among the components (which can be atomic or coupled models), through couplings. The coupling provides interaction between components. DEVS enjoys the property of closed under coupling where any coupled model can be transformed to an atomic model with identical behavior. This property supports modeling larger models in a hierarchical manner. For some purposes, models simulated in real-time, instead of step-wise or logical-time, are needed. For this purpose, the Action-Level Real-Time (ALRT) Discrete-Event System Specification (DEVS) modeling and simulation

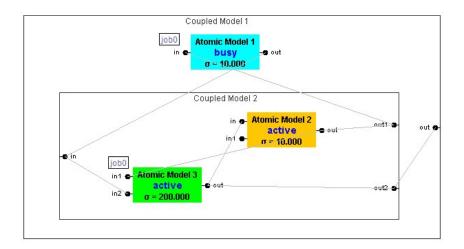

Fig. 1. Graphical notation for Atomic and Coupled Models in DEVS-Suite Simulator

formalism is developed using real-time Statecharts [26]. The internal and external transition functions for ALRT-DEVS are defined at the level of actions with time-windows which in turn support fine-grain execution as well as error handling. Actions are specified to allow execution in real-time under constrained computational resources. General-purpose DEVS models can be specialized to represent software and hardware types with mapping the former to the latter [23].

#### 2.2. DEVS-Suite Simulator

The DEVS-Suite simulator is one of the most commonly used modeling and simulation tools for the parallel DEVS formalism [39, 30, 1]. This simulator has a modeling and simulation engine. The modeling part supports implementing DEVS atomic and coupled models that have hierarchical tree-structures. The *viewableAtomic* and *viewableCoupled* Java classes allows visualization of the atomic and coupled models (see Figure 1). Both atomic and coupled models can receive input and send output entities (e.g., job0) only via separate input and output ports. Entities can strictly be transmitted via couplings between any two distinct models that are at the same level belonging to a single node in the hierarchy. The entities do not change during transmissions. The simulation part implements a message-based simulation protocol. It is responsible for executing the internals of atomic models as well as all entity transmissions among atomic and coupled models.

The simulator is developed following the Model-View-Controller (MVC) architectural style [28]. The Model conforms to the atomic and coupled model types and supports their simulation using the parallel abstract protocol [37]. The simulator can execute in logical-time. The internal and external transition functions defined according to the ALRT-DEVS formalism can be executed in near hard real-time execution. The ALRT-DEVS modeling and simulation is supported in the Parallel DEVS-Suite simulator. The FaÇade hides specific design choices and implementations of the atomic and coupled models and the abstract simulator while exposing the data and control to the Control and View. It facilitates loose coupling from Model to View and Controller. The Control provides comprehensive means to configure models and their executions including logical and near hard real-time as well as coordinating run-time simulation animation with timeview trajectories [17, 29, 40]. The View provides unique capabilities including highly flexible configurations for super-dense time-trajectories and tabular input, state, and output data which is key for large-scale model development, simulation, and debugging. The open-source simulator is developed using Java Programming language and the Eclipse BIRT plugin [1].

#### 2.3. Architecture Analysis & Design Language

Architecture Analysis & Design Language (AADL) is an SAE International standard language for the architectural description of embedded systems. It is a Model-based Engineering (MBE) approach which promotes *analyzable* architecture development that enables the dependability prediction of real-time embedded systems. MetaH [34], a prototype of the AADL, was developed by Steve Vestal at Honeywell with the aims of extensive model validation,

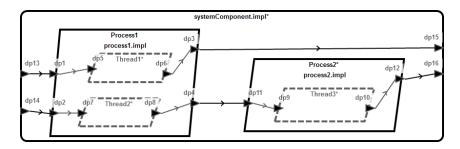

Fig. 2. Graphical notation for hierarchical modeling in AADL

better quality system design, and decreased time-to-market for the aerospace industry. MetaH is a proven concept and have been researched by both academia and industry for more than a decade.

AADL was introduced in 2004 and revised in January 2009. The latest version, AADL V2.0, available as SAE AS5506C, was revised in August 2017 [15]. AADL has been considered by embedded system designers at Honeywell, Rockwell Collins, Lockheed Martin, the European Space Agency, Airbus and other safety-critical industries. An important collaborative System Architecture Virtual Integration (SAVI) project for designing complex distributed aerospace systems has selected AADL as its architecture description language [10]. SAVI emphasizes an "Integrate, Then Build" approach—the key concept being to verify virtual integration of architectural components before implementing their internal designs. AADL supports virtual integration through an effective mechanism for component contract specification based on interfaces and interactions and through well defined semantics for extensive formal analysis at different architecture levels.

Architectural modeling in AADL is realized through component specification of both the *application software* and the *execution platform*. Component *Type* and *Implementation* classifiers, corresponding to embedded system entities are instantiated and connected together to form the system architecture model. It supports textual, graphical and XML Metadata Interchange (XMI) specification formats. Figure 2 depicts hierarchical system modeling in AADL using graphical notations.

Application software may contain *process, data, subprogram, thread,* and *thread group* components. The process component represents a protected memory space shared among thread subcomponents. A data component represents a type, local data subcomponent, or parameter of a subprogram, *i.e.*, callable code. A thread abstracts sequential control flow. In Figure 2, a composite *systemComponent* is modeled with two process components, *Process1* and *Process2*. Two thread components *Thread1* and *Thread2* are the subcomponents of *Process1* while thread *Thread3* is a subcomponent of *Process2*.

The execution platform is made up of computation and communication resources, consisting of *processor, memory*, *bus*, and *device* components. The processor represents the hardware and software responsible for thread scheduling and execution. The memory abstraction is used for describing code and data storage entities. Devices can represent either physical entities in the external environment, or interactive system components like actuators and sensors. Physical connections between execution platform components are accomplished via a bus component.

System components represent compound entities containing software, execution platform or other (sub)system components.

Open Source AADL Tool Environment (OSATE) [31] is an open source platform and toolset built on Eclipse to implement AADL for the modeling and analysis of real-time embedded systems. OSATE not only provides full-features text editor and a set of analysis plug-ins, but also supports domain-specific analysis plug-in development.

In order to furnish AADL for DEVS modeling and DEVS-Suite simulation, the core language must be extended to support continuous time-critical modeling. A DEVS behavioral annex targeted for the DEVS-Suite simulator is developed [2]. AADL data, structure, and behavior modeling is further detailed in the next section in relation with the proposed AADL-DEVS framework.

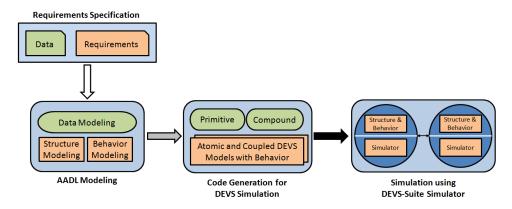

Fig. 3. AADL-DEVS Framework

#### 3. AADL-DEVS Framework

This framework is developed by integrating AADL, a semi-formal architecture description language, and DEVS, a formal discrete-event modeling & simulation language. The result supports both static and dynamic analysis and design of system architectures for safety and time-critical software-intensive system. The AADL and DEVS are specification languages where the former can be used to define possible structural system specifications, and the latter can be used to define combined structural and behavioral system specifications. Each of these languages is modular and hierarchical that makes their integration simpler. The AADL provides explicit types of abstraction for software and hardware components (i.e., nodes) and couplings (i.e., connectors). They can be used to define hybrid system specifications. The DEVS provides general-purpose components (i.e., atomic and coupled models) without the models having designated software, hardware, and hybrid.

The AADL-DEVS framework has two parts – an Annex sublanguage and a code generator for DEVS modeling and simulation. First, the AADL with its OSATE realization is extended with an Annex that conforms to the Parallel DEVS formalism and the DEVS-Suite simulator. This DEVS Annex language is specified in two parts. First, the structural syntax of atomic and coupled DEVS models are added using the OSATE language. In other words, the structural syntax in DEVS-Suite is mapped to that of the AADL syntax in OSATE. Second, the behavioral syntax of the atomic DEVS model is added using the OSATE language. The DEVS Annex structural specification accounts for the differences between the OSATE and DEVS-Suite different primitive and compound data types with different syntax declarations. The data types in DEVS-Suite, unlike their counterparts in OSATE, have behavior. In addition, the DEVS Annex language is extended to support defining the behavior of atomic models (i.e., internal and external functions) as basic state machines. Other functions that are added to DEVS Annex language are for the output and time advance functions.

The second part of the integration is for transforming AADL with DEVS Annex to parallel DEVS models. A code generation engine is developed to transform the AADL-DEVS to atomic and coupled models that can be executed in the DEVS-Suite simulator. As such, first, the AADL-DEVS models are created in OSATE, and second, the models are automatically transformed to simulation code for the DEVS-Suite simulator. In order to generate code for the simulator, it is also necessary to map the input and output primitive and compound data types in OSATE to their counterparts for the DEVS-Suite simulator. This has required two steps. First, looking from the DEVS-Suite language to the OSATE language, a set of generic I/O data types in the mold of the I/O data types are defined in DEVS Annex. Second, looking from the OSATE language to the DEVS-Suite simulator. Using the developed AADL-DEVS framework, specified parallel DEVS models can be automatically generated, loaded, and executed in the DEVS-Suite simulator. This capability empowers the AADL structural components to be simulatable.

#### 3.1. AADL Modeling

Due to its extensive support for modeling, the AADL-DEVS framework relies on AADL for modeling capability. AADL Modeling in AADL-DEVS framework is focused on Structure, Data, and Behavior modeling based on the

data and requirements identified in the requirement specification. Below we detail the structural and data modeling using AADL, while behavior modeling along with the DEVS Annex is described in Section 3.2.

#### 3.1.1. Structure Modeling

In AADL, a structural model of, an embedded system is a hierarchical composition of software and hardware components. Each component declaration incorporates component *type* and *implementation* classifiers to represent externally visible characteristics and internal realization, respectively. A component type declaration defines the interface elements and may contain *Feature*, *Flows* and *Property*. Feature normally contains communication ports. AADL supports *Data*, *Event* and *Event Data* port to transmit data, control and control and data respectively. Port communication is typed and directional. An *in* port receives data/control and an *out* port sends data/control while an *in out* port can send and receive data. A component implementation declaration defines the internal structure in terms of Subcomponents, subcomponent Connections, Subprogram call sequences, Modes, Flow implementations, and Properties. Ports of a component declared in a type declaration are connected through connections in the AADL implementation declaration.

Embedded systems are the combinations of both software and hardware required to execute the software. Software components are mapped onto execution platform components *i.e.* a thread is mapped to a processor while a data component can be mapped to a memory component. Multiple implementation classifiers can be associated to one type classifier of a specific component.

AADL provides support for both static and dynamic architectural modeling. A static architecture contains hierarchical composition of interconnected subcomponents for each containing component. These interconnected subcomponents form the internal structure of the containing component. Reconfigurable structure specification of AADL facilitates dynamic architectural modeling. Dynamic architectures are realized through modal behavior of the system. Modes contain component and connection configuration for different operational as well as error modes.

In order to support extensive and focused model analysis, AADL core language support extensions through annexes and properties.

#### 3.1.2. Data Modeling

Data modeling in AADL is accomplished through data components. Domain-specific data types are represented using the type classifier of a data component and further be detailed in the implementation classifiers. The declared data types can then be used with ports to represent the kind of data to be transmitted and data sub-components are declared to represent the data items.

AADL provides *Data Modeling Annex* with a property set and pre-defined *Base\_Types* to express data modeling in an architectural setting [14]. This annex defines more than fifteen different properties that can be used with user-defined data types (specified in terms of data components) to detail domain data element types. For data representation, the current version of the AADL to DEVS Code Generation Engine (ADCoDE) under the AADL-DEVS framework not only provides transformation support for primitive data types defined in the Base\_Types but also incorporates three commonly used compound data types. Primitive data types include *real, integer, string,* and *Boolean*. The Data Model Annex also supports *Struct* for representing compound data types. A *Struct* has multiple elements, each of which can be either of primitive or compound data types.

The primitive data types defined in AADL map directly to their counterparts in the Java programming language. For the compound data type, however, they must be defined as objects that can be operated on. This is because unlike, AADL *Struct*, simulatable model components communicate with each other using objects. An example of an input called job0 is shown in Figure 1. For any AADL compound data type that is to be either input or output, a class with data and function has to be constructed. Moreover, for any of the AADL primitive data types that is input and output, classes are also needed. For the AADL-DEVS framework, the existing classes for real, integer, and string data types are provided in the DEVS-Suite simulator. The *Integer\_Range* (used to represent a finite range of real values) and *Real\_Range* (used to represent a finite range of real values) are developed given their common utility for Safety-Critical Systems. In the DEVS-Suite simulator, all input and output (primitive or compound) are referred to as entities. For compound data type (e.g., the Isolette data types [24]), their counterparts

must be developed (see Section 6.1.). Below is an example of the data component Speed representing the speed of a train using the Data Modeling Annex.

```

1 data Speed

2 properties

3 Data_Model::Base_Type => (classifier(Base_Types::Float));

4 Data_Model::Real_Range => 200.0 .. 250.0;

5 Data_Model::Measurement_Unit => "km/h";

6 end Speed;

```

Here speed data type is of Float with possible values between 200.0 and 250.0 (a Real\_Range) and measuring unit km/h for kilometer per hour. Further details on ADCoDE are presented in Section 3.3.

#### 3.2. Behavior Modeling using DEVS Annex

This section presents the constructs of the DEVS Annex (DA), an extension to AADL for discrete-event modeling [2]. Each DA section is described in detail with its syntax, and grammar with appropriate examples. The annex subclause grammar and semantics is based on the Discrete Event System Specification (DEVS) formalism [37]. This annex brings with it the ability to model detailed behaviors at component level based the concept of the *Atomic DEVS* and at system level based on the concept of the *Coupled DEVS*, where a system is a hierarchical composition of modular components. In use, the DA subclauses can annotate any of the software and execution platform components to model the discrete behavior. The DA is expressive enough to model complex monitored and controlled variables to specify data types for ports and data items communicated through these ports.

The DEVS Annex is implemented as plug-in to an Open Source Architecture Tool Environment (OSATE) [24]. Along with full-features text editor, the OSATE can be extended with analysis plug-ins.

The rest of this section contains the Extended Backus-Naur Form (EBNF) of the DA grammar, in which: literals are printed in **bold**; alternatives are separated by a pipe |; groupings are enclosed with parentheses (); square braces [] delimit optional elements; and the closures { }+ and { }\* are used to signify one-or-more, and zero-or-more of the enclosed element, respectively. Following is the grammar of the DA subclause:

```

devs_annex ::=

[ variables { variable_declaration }+ ]

[ states state_declaration ]

[ behavior atomic_behavior_declaration ]

```

Here, the **variables**, **states**, and **behavior** are the sections of a HA subclause, each of which is dedicated to specify particular aspect of a detailed behavior model.

The DA subclauses are described in the implementation classifiers

```

1 annex devs

2 {**

3 ...

4 -- DEVS Annex sections

5 ...

6 **};

```

where annex is an AADL keyword and devs is the identifier for the DA subclause. Behavior composed of different devs sections is specified between  $\{ ** \text{ and } ** \}$ .

#### 3.2.1. Variables Section

The local variables in the scope of a DA subclause are declared in the variables section along with their data types. Data types are assigned to variables by classifier references to the appropriate AADL (user definable) data components. Each variable must have an initial value specified after =>. Depending on the data type, an initial value can either be simple (*i.e.*, integer, real, boolean, or string literal) or compound consisting of more than one simple values separated by commas and enclosed in parenthesis. Following is the grammar of the variables section:

```

variable_declaration ::=

variable_identifier :

(variable_type_identifier | data_component_classifier_reference) =>

value_declaration ;

value_declaration ::=

simple_value | compound_value

simple_value ::=

INTEGER_LIT | REAL_LIT | (true | false) | STRING

compound_value ::=

{ ( simple_value , simple_value ) }+

```

The referred external data component must either be part of the package containing the component being annotated, or must be declared within the scope of another package that has been imported using the AADL with clause. Following example shows the use of the variables section to declare different types of variables.

```

. . .

annex devs {**

3

4

variables

5

speed : Base_Types::Float => 75.0;

6

counter : Base_Type::Integer => 3

ct : Iso_Types::Temperature => (98, "Valid");

8

**};

```

Variables speed on line 5 with initial value 75.0, and counter on line 6 with initial value 3 are of type Float and Integer, respectively, and are defined in a predefined AADL package Base\_Types. Data component ct on line 7 is of type Temperature defined as structure with two elements in another AADL package Iso\_Types. Sub-statement (98, "Valid") specifies initial values for elements of variable ct; first element is of type integer initialized with 98 and second element is of type string initialized with "Valid".

Variables speed and counter are examples of variables with primitive values while ct is an example of a variable with compound value. Variables can be input or output in which case they must have their counterparts included in the DEVS-Suite simulator or constructed by the modeler (see Section 3.1.2.).

#### 3.2.2. **States Section**

1

2

7

g

All the admissible states of a particular component are defined in the states section. Each state specification has a name followed by the time advance function stating the time to remain in a particular state before next transition. States with 0 time advance function allow instantaneous transitions to the new state while states with **INFINITY** time advance function model the final state. DA only allows one starting state labeled as **initial** while the unlabeled states are considered as transient states. A complete behavior starts from an initial state, suspends in transient states (with different time advance functions) until next internal or external transition while performing actions upon each transition, and ends in the final state.

The grammar of the **states** section is as follows:

```

state_declaration ::=

```

```

state_identifier : [ initial ]

( REAL_LIT | INFINITY | variable_identifier ) ;

```

Following example shows the use of **states** section to declare different types of constants.

```

1 ...

2 annex devs {**

3 ...

4 states

5 Start: initial 0.0;

6 Chk_Busy: 3.0;

7 Busy: period;

8 Passive: INFINITY;

9 ...

10 **};

```

Starting state start on line 5 is declared as initial and with time advance function 0.0. State chk\_Busy on line 6 is a transient state with time advance function 3.0 indicates that the system will suspend in this state for 3.0 time units. The system can stay in Busy on line 7 state for period time units. Time variable period is declared in the variable section not shown here. State Passive on line 8 with time advance function INFINITY specifies a final state.

#### 3.2.3. Behavior Section

The behavior section of the DA subclause is used to specify the discrete behavior of annotated AADL component in terms of a state-transition system with three functions and one declaration. The functions deltext and deltint are used to specify external and internal transitions, respectively. The function outfn specifies the system's output based on the change in total state, either due to external or internal state transition. The test inputs for stand-alone testing are specified using the intest declaration. The time advance function that can specify the time periods for state transitions (i.e., deltext and deltint functions) is excluded. This decision is made for simplicity and time period used in the state transition functions are generally as given as values, not computed as functions. All the identifiers used in this must refer to the declarations defined in their respective sections.

The grammar of the **behavior** section is as follows.

```

atomic_behavior_declaration ::=

deltext external_transition_declaration |

deltint internal_transition_declaration |

outfn outfn_declaration |

intest intest_declaration

```

Below, we explain each of these functions which may constitute a component's behavior individually or in combination with other functions.<sup>1</sup>

#### 3.2.4. External Transition Function

The function deltext is used to model the external transition caused by an input message from a source state. This external message interrupts system's behavior moving it to the destination state. The system's response to external messages is specified as *behavior action* and depends on the current state, specific input, and the time elapsed in current state.

An external message in DA sublanguage is composed of the respective port name, the value received, and a variable to store this value for future local use. It is important to note that type of the variable must match with data classifier specified along the port in the type classifier.

<sup>&</sup>lt;sup>1</sup>A complete DEVS Annex syntax card with detailed grammar productions are described in Appendix A1.

The behavior action in DA sublanguage specifies the activities to be performed upon completion of the external transition. Current version of the sublanguage uses a string to model these actions and should contain syntactically correct Java language statements. Extension of the sublanguage to allow common Java constructs is an important future work in this direction.

Below is the grammar of the **deltext**.

```

external_transition_declaration ::=

deltext [ source_state_identifier , message ]->

destination_state_identifier behavior_action

message::=

port_identifier (? | !) variable_identifier ;

behavior_action ::=

{ STRING }

```

Following example shows the use of deltext function to specify external transitions.

```

. . .

2

annex devs {**

3

4

behavior

5

deltext [Active, get?iVar]-> Passive {};

deltext [Speed, spin?pVar]-> Busy {

6

7

if (pVar > 0 && position < EoA)

8

status = "Valid";

9

else

10

status = "Invalid"; "

11

};

12

13

**};

```

\*\*\*\* CHECK PAGE Numbering

The function deltext defined on line 5 specifies an external transition with Active as source state. On receiving an event on get in port, the system behaves as destination state Passive. No behavior action is defined along with this external transition as indicated by empty braces. External transition function defined on line 6 specifies that while in the Speed state, if a message is received on spin in port the received value is stored in variable pVar. The behavior action is composed of an if-else statement and Busy is the destination. Variables iVar, pVar, position, EOA, and status are defined in the variables section (not shown here) while in ports get, and spin are defined in type classifier (not shown here) of the respective component.

#### 3.2.5. Internal Transition Function

Function deltint is used to model the internal transition caused by progression of the elapsed time (e) to time to make transition to the next state (specified as time advance function) ta, when e = ta. Target state identifier follows the source state identifier and is followed by the behavior action specification. As mentioned earlier, current version of the sublanguage uses a string to model these actions and should contain syntactically correct Java language statements.

Below is the grammar of the **deltint** function.

```

internal_transition_declaration ::=

deltint [ source_state_identifier ]->

destination_state_identifier behavior_action ;

```

Following example shows the use of deltint function to specify internal transitions.

1 | . . .

```

2

annex devs {**

3

4

5

states

Ready: initial 0.0;

6

7

Busy: period;

Passive: INFINITY:

8

9

behavior

10

deltint [Ready] -> Busy {"count=count+1;"};

11

deltint [Busy] -> Passive {};

12

13

**};

```

Function deltint defined on line 10 specifies an instantaneous (as ta=0.0 on line 5) internal transition from source state Ready to the destination state Busy state. Behavior action for this transition specifies increment to a *count* variable declared in the variables section (not shown here). Function deltint defined on line 11 specifies an internal transition with Busy source state and Passive as destination state. This transition will occur as soon as the elapsed time *e* equals to period (*ta* for Busy state). Variable period is defined in the variables section which is not shown here. State Passive on line 7 *ta* equals to INFINITY is the end state.

#### 3.2.6. Output Function

The ounction **outfn** is used to model observable outputs. Output messages are only generated on internal transitions before the state change. If an output is required to be generated on an external transitions, the control must be moved to a state with ta = 0.0 for output triggering followed by an instantaneous internal transition to the actual destination state. An output message contains name of the out port followed by ! sign and the data to be transmitted. Type of the data must comply with the type of the port defined in the type classifier. An **outfn** specification may also contain conditional expression to further restrict output generation. A conditional expression is made up of boolean terms combined using relational operators while the numeric expressions are defined to specify arithmetic operations (+, -, \*, /, mod) and the power operation ( $\land$ ).

Below is the grammar of the **outfn** function.

```

outfn_declaration ::=

outfn [ source_state_identifier [ , conditional_expression ] ]-> message

behavior_action ;

conditional_expression ::=

boolean_term [ and boolean_term [ and boolean_term ] |

or boolean_term [ or boolean_term ] ]

boolean_term::=

[ not ] [ variable_identifier | [ boolean_expression ] | relation ]

relation::=

( numeric_expression ( ==| !=| >| <| >=| <= ) numeric_expression )</pre>

```

Following example shows the use of out fn function to specify output generation.

Function outfn defined on line 5 specifies an output function generated from from state Running. The value of a speed variable is transmitted through output port op whenever the e=ta for state Running and boolean variable isValid is true. Function outfn on line 6 models the output generation from state Stop. Real value 0.0 is transmitted through output port op whenever the e=ta for state Stop without any further condition.

#### 3.2.7. Test Input Declaration

Declaration intest is used to specify the input to be used for stand alone testing during simulation<sup>2</sup>.

It is not part of the DEVS formalism rather used by the DEVS-Suite (the target simulator) for injecting test input for model components. This input declaration specification contains input port name followed by the value. Simple values are specified directly and compound values (the one with multiple data items) are parenthesized while separating data items with commas, and organizing them in order.

```

intest_declaration ::=

intest [ port_identifier , value_declaration ] ;

```

Following example shows the use of **intest** declaration to specify dynamic input usage.

```

1 ...

2 annex devs {**

3 ...

4 behavior

5 intest [status, true];

6 intest [temperature, (98.0, "Valid")];

7

8 ...

9 **};

```

The declaration intest on line 5 specifies an input with input port status and the value true. The test input declaration intest defined on line 6 specifies an input for dynamic application on input port temperature. The input is expressive enough to have compound inputs. The value to be applied has two data items; the first is of type real with value 98.0 and the second is of type string with value Valid.

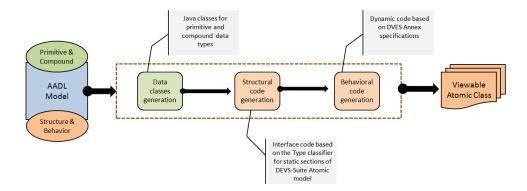

#### 3.3. Code Generation for Simulation

*Code generation for DEVS simulation* is the third phase of the proposed DEVS-AADL model. As DEVS-Suite, being one of the most commonly used DEVS modeling and simulation toolset, has been selected for simulation, this phase is focused on transformation from AADL models with DA specification into DEVS-Suite specifications.

DA is implemented as domain specific language (DSL) for behavior specification that is later to be simulated using DEVS-Suite simulator. Although structure of the DA sublanguage is based on DEVS theory but DA specifications are still not executable under DEVS-Suite. For efficient and valid simulation, it is required to generate appropriate DEVS-Suite code, as Java classes, from DA specifications in each section. To ease complex behavior modeling DA seamlessly integrates with AADL core language and does not require re-definition of the interface elements defined in the type classifier of the respective component. Reliance on AADL core language for structural and data modeling further intensifies the challenge of DEVS-Suite code generation from the DA specifications. To cope with this challenge, we have implemented ADCoDE—an AADL to DEVS CoDe generation Engine. ADCoDE is implemented as a plug-in to OSATE and can be activated for an implementation classifier (annotated with DA specifications) of a particular component selected in Eclipse Outline view. An Xtend file *DevsGenerator.xtend* contains the main class with methods responsible for code generation by traversing the type and implementation classifier of the selected component.

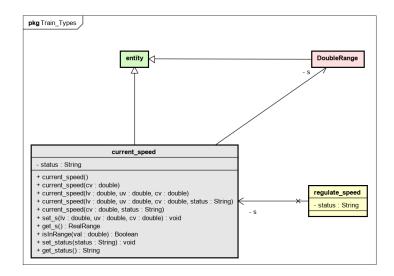

As depicted in Figure 4, upon activation for a particular AADL component with detailed data, structure, and behavior modeling using DA sublanguage, code generation through ADCoDE is a three step process. Firstly, in the *data classes generation* step, appropriate Java classes are generated for primitive and compound data types. Secondly, in the *structural code generation* step, structural and interface code for input and output ports is generated based on the type classifier of the AADL component. Thirdly, in the *behavioral code generation*, behavioral code is generated based on the DA specifications in the particular component. All the generated code segments are then structured to form a ViewableAtomic class ready to be simulated in the DEVS-Suite simulator. Code generation for one AADL component results in one ViewableAtomic class. All the ViewableAtomic classes generated for several components in an AADL package are organized in the *Model* folder while the generated data classes are organized.

<sup>&</sup>lt;sup>2</sup>The keyword infn, as used in an earlier version of the DEVS Annex introduced in [2], is now replaced with the **intest** to improve readability and understanding

Fig. 4. AADL to DEVS Code Generation Engine (ADCoDE) Workflow

in a separate folder named same as the AADL package in which the data components are defined. Contents of all these folders are dynamically updated on any new data or ViewableAtomic class generation. This hierarchical organization of the generated code not only improves designer's understanding at the modeling level but also ease the selection and monitoring of atomic and coupled models during simulation.

ADCoDE also realizes code generation for couple DEVS models. Upon activation for a composite AADL component (for example a thread group), a model class extending the ViewableDigraph is generated along with required data and model classes for each AADL sub-component(thread components). Below we explain three step codegeneration process of the ADCoDE with appropriate examples while code generation for couple DEVS models in further detailed in Section 3.3.4.

#### 3.3.1. Data Classes Generation

As explained in Section 3.1.2., AADL allows both primitive and compound data types for data modeling, hence the ADCoDE must also have the capability to map them with respective DEVS-Suite data types. As primitive data types, pre-defined in the Data Modeling Annex and Base\_Types, directly map to the basic data types in DEVS-Suite, the core of the DEVS-Suite also needs to be extended. Such an extension must be realized via inheriting from the *Entity* class as DEVS-Suite only allows transmitting objects (messages sent and received) either Entity or any of its subclasses.

As noted in Section 2.2., AADL to DEVS transformation requires the AADL data types representing input and output to be mapped to entity data types. The input and output entities are the events sent and received among atomic and coupled models.

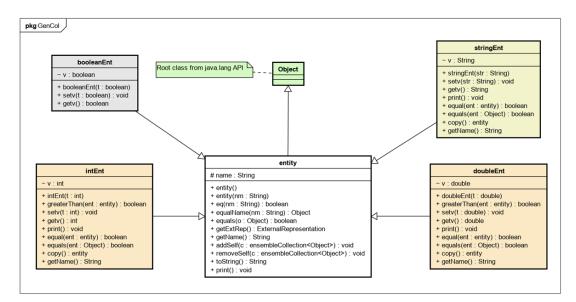

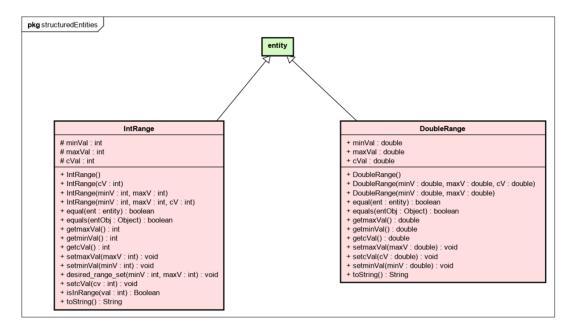

Figure 5 shows the extension of the Entity class for AADL primitive data types. These classes include the primitive **stringEnt**, **booleanEnt**, **intEnt**, and **doubleEnt** data types for their AADL *String*, *Boolean*, *Integer*, *Float* counterparts. Every class has a private variable v of the respective primitive type. Each class further includes getv(), and setv() as getter and setter for the private variable v, respectively, and method print() to print and method copy() to copy current value of variable v. Methods equal() and equals() are to compare an entity and an object of the respective type while method getName() outputs the name of the object.

Below is an example of the primitive data type Integer declared in the Base\_Types (as on line 3) and the corresponding DEVS-Suite code generated by the ADCoDE for a variable pd declared in the variables section of a DA specification (as on line 11). It is important to note that no new Java class is generated by the ADCoDE for primitive data types while the corresponding objects of respective subclasses are generated (as on line 15).

```

1

2

3

4

5

6

7

8

9

```

```

-- Integer data type declaration in Base_Types

data Integer

properties

Data_Model::Data_Representation => Integer;

end Integer;

...

-- Variable declaration in DA specification with Integer data type

```

Fig. 5. Class diagram for primitive data types

Fig. 6. Class diagram for compound data types

```

10 variables

11 pd : Base_Types::Integer => 100;

12

13 ...

14 -- Code generated by ADCoDE for ViewableAtomic class

15 private intEnt pd;

16

17 ...

```

The core of the DEVS-Suite simulator has also been extended with new classes to incorporate with complex data types for data modeling. Figure 6 depicts the class diagram showing the Entity class extension for complex data types. The classes IntRange and DoubleRange are defined for the Integer\_Range, and Real\_Range datatypes, respectively. Each of these classes has three private variables; minVal, maxVal, and cVal representing minimum, maximum, and current values, respectively. For initialization, objects of these classes along with the values for the variables are automatically extracted from their respective models during code generation. Aside from a default constructor, there are constructors that can have minVal, maxVal, and cVal as input arguments. Each class includes getters and setters such as getminVal() for retrieving the minVal variable. The method toString() returns string representation of the object. The methods equal() and equals() are to compare an entity with its corresponding object types. For each complex data type used in an AADL component's type or implementation classifier, a separate Java class is generated.